level 12

胡杨胖子

楼主

3C501是第一块用于X86平台的ISA网卡,剖析下它的原理有助于帮助我们了解网卡是如何工作的。

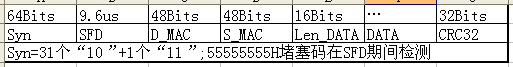

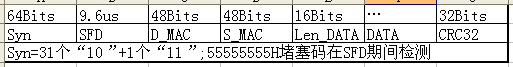

网卡采用带同步信号的曼彻斯特编码(具体含义请BD该名词),其具体每组数据包的格式如下——(目前网络速度大幅提高,SFD已经改变了)

冲突检测使用CSMA/CD载波侦听的介质层协议(具体名词含义请BD)。

冲突检测使用CSMA/CD载波侦听的介质层协议(具体名词含义请BD)。

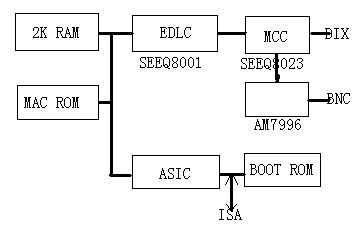

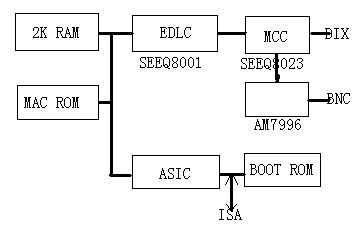

3C501网卡的具体方块图如下——

EDLC为数据链路控制芯片、MCC为曼彻斯特码编码器、ASCI为ISA接口逻辑电路,3C501通常占用300~30F共16个I/O口,实际上使用308~30F这几个,对应的寄存器及I/O口如下——

EDLC为数据链路控制芯片、MCC为曼彻斯特码编码器、ASCI为ISA接口逻辑电路,3C501通常占用300~30F共16个I/O口,实际上使用308~30F这几个,对应的寄存器及I/O口如下——

下面我们将介绍具体介绍个寄存器的作用,并分析网络分组包的收发过程(待续)

下面我们将介绍具体介绍个寄存器的作用,并分析网络分组包的收发过程(待续)

2013年04月06日 09点04分

1

网卡采用带同步信号的曼彻斯特编码(具体含义请BD该名词),其具体每组数据包的格式如下——(目前网络速度大幅提高,SFD已经改变了)

冲突检测使用CSMA/CD载波侦听的介质层协议(具体名词含义请BD)。

冲突检测使用CSMA/CD载波侦听的介质层协议(具体名词含义请BD)。3C501网卡的具体方块图如下——

EDLC为数据链路控制芯片、MCC为曼彻斯特码编码器、ASCI为ISA接口逻辑电路,3C501通常占用300~30F共16个I/O口,实际上使用308~30F这几个,对应的寄存器及I/O口如下——

EDLC为数据链路控制芯片、MCC为曼彻斯特码编码器、ASCI为ISA接口逻辑电路,3C501通常占用300~30F共16个I/O口,实际上使用308~30F这几个,对应的寄存器及I/O口如下——

下面我们将介绍具体介绍个寄存器的作用,并分析网络分组包的收发过程(待续)

下面我们将介绍具体介绍个寄存器的作用,并分析网络分组包的收发过程(待续)